#### 1. MOSFETの構造、品質向上について

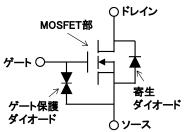

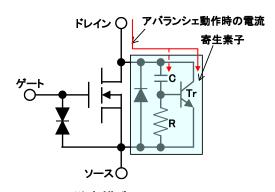

MOSFETの等価回路は一般的には図1のようになり、当社のデータシートにも記載しております。

以下、各部について説明します。

# (1)MOSFET部

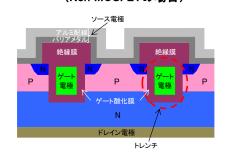

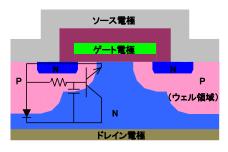

当社MOSFETは、パターンの微細化が可能なトレンチ構造を採用しております。概略の断面図を図2に示します。

トレンチ構造は、図2に示しますように、シリコン表面に溝(トレンチ)を形成して、その側壁をチャンネルとして使用する構造です。この構造はパターンの微細化が可能であり、従来のDMOS構造の場合よりも小さいチップサイズで低いON抵抗を実現することが可能です。

また、当社では、ソース電極をバリアメタルとアルミの2 層構造としており、品質信頼性の向上を図っております。

図1 MOSFET等価回路 (Nch MOSFETの場合)

図2 トレンチ構造断面図 (Nch MOSFETの場合)

#### (2)ゲート保護ダイオード

MOSFETの、ゲート酸化膜の静電破壊保護用として、ゲート・ソース間に設けており、VGSSはこの保護ダイオードの逆耐圧で決定されます。

この保護ダイオードは、MOSFETの取り扱いの際の静電気保護用を目的としておりますので、実機状態でのサージ吸収用途には、ツェナーダイオード等を外付けでご使用されることを推奨致します。

なお、当社では、静電破壊耐量をより大きくするために、ゲートに抵抗を付加した製品も開発しております。詳細は、当社営業担当者へご相談下さい。

# (3) 寄生ダイオード

MOSFETの構造上、ドレイン・ソース間に形成されるダイオードです。したがって、ドレイン・ソース間には逆電圧をかけることは出来ません。

また、このダイオードは順方向へ電流を流すことは意図しておりませんので、回路上でダイオードが必要な場合は、別途ダイオードを外付けでご使用されることを推奨致します。

# ご使用上の注意~MOSFET編~

#### 2. MOSFETの駆動電圧について

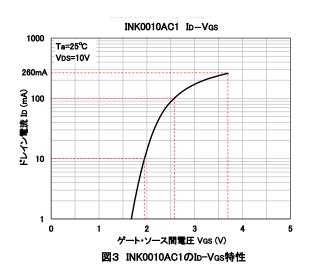

当社では、MOSFETの駆動電圧として、定格電流IDを流すことが可能な最小の電圧としています。 したがって、お客様の回路上で流す電流が小さい場合は、駆動電圧で定義している電圧以下でのご 使用が可能となります。本件について、INK0010AC1の場合を例として説明致します。

INK0010AC1のID-VGS特性を図3に示します。 図3より、INK0010AC1のIDの定格は260mAで すが、100mA程度の電流でれば、VGS=3Vでも 対応可能であり、ID=10mAであればVGS=2.5V でも対応可能であることが判ります。

その他の品種についても、同様に、ご使用される電流によって駆動電圧も変わりますので、 ご不明な点がございましたら、当社営業担当者 へご相談下さい。

#### 3. Ze内蔵MOSFETについて

# (1)アバランシェ破壊とは

MOSFETで誘導性負荷を駆動する場合に、スイッチング動作オフ時の逆起電力によって生じるサージ電圧がドレイン-ソース間電圧VDSSを超えてMOSFETがブレークダウンする際に、アバランシェ破壊が発生する場合があります。

MOSFETは、構造上図5のような寄生素子(バイポーラトランジスタ/Tr、抵抗/R、コンデンサ/C)が形成されています。

アバランシェ動作の際は、図5に破線で示すような電流が寄生容量Cを通して流れることになり、抵抗Rの両端の電位がトランジスタTrのベース・エミッタ電圧を超えた場合にTrがONします。

この時に、Trに過大な電流が流れることにより、 MOSFETが破壊することになります。

この現象をアバランシェ破壊と呼んでいます。

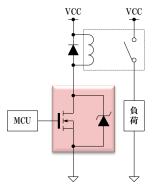

図4 誘導性負荷の駆動回路

図5 従来構造のMOSFET

### (2)アバランシェ耐量向上対策

アバランシェ耐量を向上させるためには、前述した寄生トランジスタ/Trを動作しにくくする必要があります。

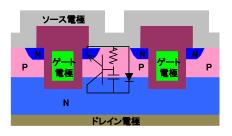

従来のDMOS構造の場合は、この対策として、寄生抵抗/R を低減する方法を取っております。

ー例として、従来のDMOS製品の断面構造を図6に示します。 同図に示しますように、ウェル領域を深くすることにより寄生抵抗/Rを小さくしております。

MOSFETの性能向上(ON抵抗低減等)を進める場合は、パターンの微細化が必要であり、現在は、より微細化が可能なトレンチ構造のMOSFETが主流となっております。

トレンチ構造の場合は、上記したDMOS構造のような対策が 取りにくいため、別の方策が必要となっております。

図6 DMOS構造

図7 トレンチ構造

# ご使用上の注意~MOSFET編~

#### (3)Ze内蔵MOSFET開発

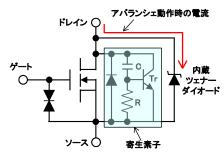

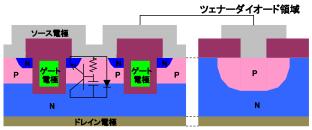

当社では、アバランシェ耐量向上対策として、図8に示しますように、MOSFETのドレイン・ソース間に、VDSSよりも低い電圧でブレークダウンするツェナーダイオードを取り付けております。

この場合、アバランシェ動作の際は、寄生素子に電流が流れる前に、ツェナーダイオードを介して電流が流れることにより、寄生トランジスタTrがONしにくくなっております。

また、このツェナーダイオードは、MOSFETと 同一チップ内に構成することにより、3ピンの 小型パッケージへの搭載を可能としました。

図8 ツェナーダイオード内蔵MOSFET

図9 ツェナーダイオード内蔵MOSFET断面構造

# (4)Ze内蔵MOSFETラインナップ

現在、下記2品種の開発が完了し、量産しております。

これ以外の電圧、電流規格の製品につきましても、ご要望がある場合は開発を検討致します。

|            | VDSS(V) | Vgss(V) | ID(A) | Vth(V)  | Ron(Ω) | パッケージ |

|------------|---------|---------|-------|---------|--------|-------|

| INKE111AC1 | 50±10   | ±20     | 0.5   | 1.0~2.0 | 0.6    | SC-59 |

| INKE211AC1 | 50±10   | ±20     | 1.0   | 1.0~2.0 | 0.3    | SC-59 |

サンプルのご要求につきましては、当社営業担当者にお問い合わせお願い致します。