#### ■ 特徴 **Feature**

# 複数の受動部品、能動部品等で構成された回路(機能)ブロックをワン・パ ッケージ化することで、機器の小型、軽量化、品質向上が実現できます。

Making single circuit (function) block made up of multiple passive parts, active parts and etc., into one package, enables reducing the size, weight and quality of the equipment.

#### ☑ 小型、省配線、軽量化の実現

Compact size, reduced wiring and lighter weight

#### ☑ 実装部品点数の削減による部品調達、組立工数の削減

Reduces parts procurements and assembly man-hours by reducing the number of mounted parts.

#### ☑ 設計標準化による設計開発工期の短縮

Reduction of design development time by design standardization

#### **Technical Elements** ■ 技術要素

# ✓ パッケージ技術 Package

お客様の実装エリアに最適なパッケージプロセスを保有しております。

We have the optimal packaging process for customer's mounting area.

- · · · 小面積、大電流 small area, high current · SIL (Single inline package)

- · ZIL (Zigzag inline package) ・・・・ 小面積、多ピン small area, high-pin-count

- · DIL (Dual inline package) · · · 低背 low height

# ☑ ベアチップ実装 Chip on board

複数のベアチップを基板上に実装することが可能です。

また、リバースプロセスにも対応しており、面実装部品との高密度実装が可能です。

Multiple bare chips can be mounted on the board.

It also supports the reverse process, enabling high density mounting with surface mounted components.

# ☑ トリミング Trimming

レーザートリミング機を導入しており、電気特性の精度を上げることが可能です。

We have introduced a laser trimming machine and it is possible to increase the accuracy of electrical characteristics.

#### □ コーティング Coating

樹脂コーティングすることで、機密保持化に有効で、耐硫化ガスにも効果が期待 できます。

The resin coating is effective in maintaining confidentiality and also improves sulfur gas resistance.

# ☑ テスト技術 Test system

最終検査用の電気テスターを自社で開発し、高品質な製品を提供できます。

We are capable of delivering high-quality products by developing our own electrical tester for final inspection.

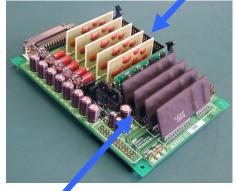

# ■ 製品事例 Product examples

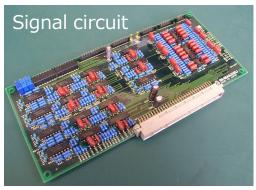

### **Before**

実装面積(size): 44,000mm<sup>2</sup>

部品点数(number of parts): 693pcs

Number of circuits=10

Number of circuits=10

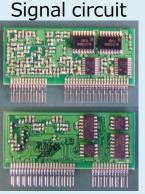

### **After**

実装面積(size): 14,500mm<sup>2</sup>

部品点数(number of parts): 63pcs

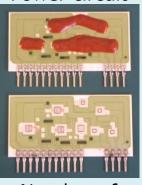

Power circuit Hics = 5pcs

# **Hybrid IC**

Power circuit

Number of circuits=2

Number of circuits=2

Signal circuit Hics = 5pcs

面積(size) ≒ 1/3 部品点数(number of parts) ≒ 1/10

# ■ 標準パッケージ Standard Package

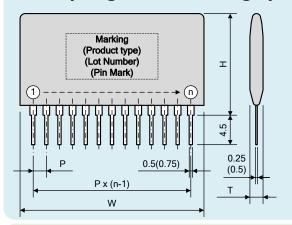

# **♦SIP** (Single Inline Package)

| Terminal pitch | Р | 1.8, 2.0, 2.54 mm                                  |

|----------------|---|----------------------------------------------------|

| Terminal Num.  | n | Max 38 (2.54mm)                                    |

| Width          | W | 10~100mm                                           |

| Height         | Н | 15~50mm                                            |

| Thickness      | Т | 6mm~                                               |

| PWB            | - | FR-4 or CEM-3<br>or Al <sub>2</sub> O <sub>2</sub> |

| Coating        | - | Ероху                                              |

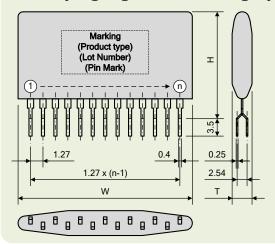

## **♦ZIP** (Zigzag Inline Package)

| Terminal pitch | Р | 1.27 mm                                            |

|----------------|---|----------------------------------------------------|

| Terminal Num.  | n | Max 76                                             |

| Width          | W | 10~100mm                                           |

| Height         | Н | 15~50mm                                            |

| Thickness      | Т | 6mm~                                               |

| PWB            | - | FR-4 or CEM-3<br>or Al <sub>2</sub> O <sub>2</sub> |

| Coating        | - | Ероху                                              |

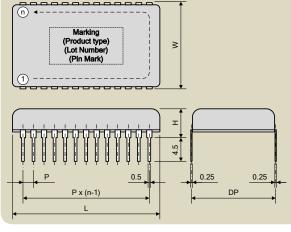

# **◆DIP** ( Dual Inline Package )

| Terminal pitch | P | 1.8, 2.0, 2.54 mm                                  |

|----------------|---|----------------------------------------------------|

| Terminal Num.  | n | Max 76 (2.54mm)                                    |

| Width          | W | 20~40mm                                            |

| Height         | Н | 5mm~                                               |

| Length         | L | 20~100mm                                           |

| PWB            | - | FR-4 or CEM-3<br>or Al <sub>2</sub> O <sub>2</sub> |

| Coating        | - | Ероху                                              |

### ※この他の形状につきましては、ご相談させてください。

Other requests regarding the shape are welcome for consultation.

# ■ 製造プロセス Manufacturing process

# 【特徴】 ☑ 基板上にベアチップ実装が可能(COB)

Bare chip mounting possible on board

#### ☑ リバースプロセスによる高密度実装が可能

High-density mounting by reverse process is possible

#### ☑ レーザートリミングによる、電気特性の微調整が可能

Fine tuning of electric characteristics by laser trimming

クリーンルーム Clean Room

## 基板(PWB)

#### ダイボンド Die Bonding

ICやトランジスタ等のベアチ ップを基板に搭載します。 Mounting of bare chips such as transistors and IC on the board

Wire Bonding

ベアチップの電極と基板の電 極を金線で接続します。 Connecting bare chips and board with gold wires.

プリコート Pre-Coating

保護のため樹脂でコーティ ングします。 Coating with resin for protection.

はんだ印刷 Solder Printing

基板にはんだペースト を印刷します。 Printing solder paste on board.

チップマウント Chip Mounting

はんだ印刷された基板に 電子部品を搭載します。 Mounting electrical components on printed board.

## リフロ・ Reflow

はんだを溶融し部品と基板 の電極を接続します。 Melt the solder to connect the electrical components to the

## 目視検査 **Visual Examination**

部品のはんだ付け状態を 検査します。 Examination of products after soldering.

### トリミング Trimming

素子や回路のバラつきを トリミングで補正します。 Trimming to correct any possible misalignments.

#### リードクランフ **Lead Clamping**

基板にリードを取付けます。 Attaching leads to the board by clamping.

#### 洗浄 Cleaning

基板に付着したフラックス を除去します。 Removing flux from the board.

樹脂でコーティングします。 Applying outer resin coating.

Marking

number.

製品名、ロットNo等を印 字します。 Marking of P/N and lot

リードカット **Lead Cut**

リードのタイバーを切断し、 個片にします。 Cutting the excess lead tie bar.

電気外観検査 **Electrical Examination**

電気特性と外観の検査を 全数行います。 Examination of electrical characteristics and outer appearance.

梱包·出荷 Packaging & Shipping